# Interrupt Timed Automata: Verification and Expressiveness

Béatrice Bérard · Serge Haddad · Mathieu Sassolas

Wednesday 21st December, 2011

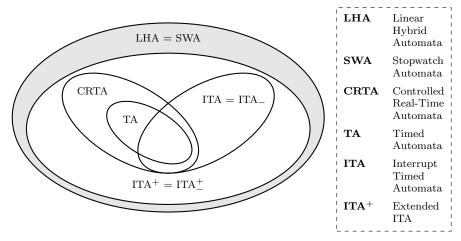

**Abstract** We introduce the class of Interrupt Timed Automata (ITA), a subclass of hybrid automata well suited to the description of timed multi-task systems with interruptions in a single processor environment.

While the reachability problem is undecidable for hybrid automata we show that it is decidable for ITA. More precisely we prove that the untimed language of an ITA is regular, by building a finite automaton as a generalized class graph. We then establish that the reachability problem for ITA is in NEXPTIME and in PTIME when the number of clocks is fixed. To prove the first result, we define a subclass ITA\_ of ITA, and show that (1) any ITA can be reduced to a language-equivalent automaton in ITA\_ and (2) the reachability problem in this subclass is in NEXPTIME (without any class graph).

In the next step, we investigate the verification of real time properties over ITA. We prove that model checking SCL, a fragment of a timed linear time logic, is undecidable. On the other hand, we give model checking procedures for two fragments of timed branching time logic.

We also compare the expressive power of classical timed automata and ITA and prove that the corresponding families of accepted languages are incomparable. The result also holds for languages accepted by controlled real-time automata (CRTA), that extend timed automata. We finally combine ITA with CRTA, in a model which encompasses both classes and show that the reachability problem is still decidable. Additionally we show that the languages of ITA are neither closed under complementation nor under intersection.

**Keywords** Hybrid automata, timed automata, multi-task systems, interrupts, decidability of reachability, model checking, real-time properties.

Parts of this paper have been published in the proceedings of FoSSaCS'09 [9] and Time'10 [10]

Béatrice Bérard · Mathieu Sassolas

Université Pierre & Marie Curie, LIP6/MoVe, CNRS UMR 7606, Paris, France

E-mail: {beatrice.berard | mathieu.sassolas}@lip6.fr

Serge Haddad

École Normale Supérieure de Cachan, LSV, CNRS UMR 8643, INRIA, Cachan, France

E-mail: haddad@lsv.ens-cachan.fr

#### 1 Introduction

#### 1.1 Context

The model of timed automata (TA), introduced in [4], has proved very successful due to the decidability of several important verification problems including reachability and model checking. A timed automaton consists of a finite automaton equipped with real valued variables, called clocks, which evolve synchronously with time, during the sojourn in states. When a discrete transition occurs, clocks can be tested by guards, which compare their values with constants, and reset. The decidability results were obtained through the construction of a finite partition of the state space into regions, leading to a finite graph which is time-abstract bisimilar to the original transition system, thus preserving reachability.

Consider several tasks executing on a single processor (possibly scheduled beforehand, although this step is beyond the scope of this paper). As a result, tasks are intertwined and may interrupt one another [37]. Since the behaviour of such systems may depend on the current execution times of the tasks, a timed model should measure these execution times, which involves clock suspension in case of interruptions. Unfortunately, timed automata lack this feature of clock suspension, hence more expressive models should be considered.

Hybrid automata (HA) have subsequently been proposed as an extension of timed automata [30], with the aim to increase the expressive power of the model. In this model, clocks are replaced by variables which evolve according to a differential equation. Furthermore, guards consist of more general constraints on the variables and resets are extended into (possibly non deterministic) updates. This model is very expressive, but reachability is undecidable in HA. The simpler model obtained by allowing clocks to be stopped and resumed, stopwatch automata (SWA), would be sufficient to model task interruptions in a processor. However, reachability is also undecidable for SWA [18]. Many classes have been defined, between timed and hybrid automata, to obtain the decidability of this problem.

Task automata [23] and suspension automata [31] model explicitly the scheduling of processes. Some classes restrict the use of variation of clock rate in hybrid automata to achieve decidability. Examples of such classes are systems with piece-wise constant derivatives [6], controlled real-time automata [21]. Guards may also be restricted, as in multi-rate or rectangular automata [3], some integration graphs [26], or polygonal hybrid systems [7]. Restricting reset may also lead to decidability as in the hybrid automata with strong resets [13] or initialized stopwatch automata [24]. O-minimal hybrid systems [28,29] provide algebraic constraints on hybrid systems to yield decidability. Extensions of timed automata to release some constraints were also considered, as in some updatable timed automata [12].

While untimed properties like reachability and LTL [33,38] or CTL model checking [22,34,19], are useful for such models, real time verification consider more precise requirements, for instance quantitative response time properties. Therefore, timed extensions of these logics have been defined. In the case of linear time logics, verification of the most natural extension MTL [27] is undecidable on TA. However, several decidable fragments such as MITL [5] and SCL [35] have subsequently been defined. In the case of timed variants of branching time logics, different versions of Timed CTL (TCTL) [2,25] have been defined. Model checking procedures on TA for both versions of TCTL have been developed and implemented in several tools [8,15].

#### 1.2 Contributions

In this paper, we define a subclass of hybrid automata, called Interrupt Timed Automata (ITA), well suited to the description of multi-task systems with interruptions in a single processor environment.

The ITA model. In an ITA, the finite set of control states is organized according to interrupt levels, ranging from 1 to n, with exactly one active clock for a given level. The clocks from lower levels are suspended and those from higher levels are not yet defined (thus have arbitrary value 0). On the transitions, guards are linear constraints using only clocks from the current level or the levels below and the relevant clocks can be updated by linear expressions, using clocks from lower levels. Finally, each state has a policy (lazy, urgent or delayed) that rules the sojourn time. This model is rather expressive since it combines variables with rate 1 or 0 (usually called stopwatches) and linear expressions for guards or updates. The ITA model is formally defined in Section 2.

Reachability problem. As said before, the reachability problem is undecidable for automata with stopwatches [24,18,16]. However, we prove that it is decidable for ITA.

More precisely, we first show that the untimed language of an ITA is effectively regular (Section 3). The corresponding procedure significantly extends the classical region construction of [4] by associating with each state a family of orderings over linear expressions. This construction yields a decision algorithm for reachability in 2-EXPTIME, and PTIME when the number of clocks is fixed. This should be compared to TA with 3 clocks for which reachability is PSPACE complete [20].

We define a slight restriction of the model, namely ITA\_, which forbids updates of clocks other than the one of the current level. We prove that for any ITA one can build an equivalent ITA\_ w.r.t. language equivalence, whose size is at most exponential w.r.t. the size of the ITA and polynomial when the number of clocks is fixed. Based on the existence of a bound for the length of the minimal reachability path, we then show that reachability on ITA\_ can be decided in NEXPTIME without any class graph construction. This yields a NEXPTIME procedure for reachability in ITA (Section 4).

Model checking over ITA. We then focus on the verification of real time properties for ITA (Section 5), expressed in timed extensions of LTL and CTL.

First we show that the model checking of timed (linear time) logic MITL [5] is undecidable. Actually, even the fragment SCL [35] cannot be verified on ITA, while the corresponding verification problem over TA is PSPACE-complete.

We then consider two fragments of the timed (branching time) logic TCTL, introduced in [25] and also studied later from the expressiveness point of view [14]. The first one,  $\mathsf{TCTL}_c^{\mathrm{int}}$ , contains formulas involving comparisons of model clocks as atomic propositions. In this logic, it is possible to express properties like: (P1) a safe state is reached before spending 3 t.u. in handling some interruption. Decidability is obtained by a generalized class graph construction in 2-EXPTIME (PTIME if the number of clocks is fixed). Since the corresponding fragment cannot refer to global time, we consider a second fragment,  $\mathsf{TCTL}_p$ , in which we can reason on minimal or maximal delays. Properties like (P2) the system is error free for at least 50 t.u. or (P3) the system will reach a safe state within 7 t.u. can be expressed. In this case, the decidability procedure

has a complexity in NEXPTIME for the existential fragment and 2-EXPTIME for the universal fragment (respectively NP and co-NP if the number of clocks is fixed).

Expressiveness. We also study the expressive power of the class ITA (Section 6), in comparison with the original model of timed automata and the more general controlled real-time automata (CRTA) proposed in [21]. In CRTA, clocks and states are colored and a time rate is associated with every state. During the visit of a state, all clocks colored by the color of the state evolve with the state rate while the others do not evolve. We prove that the corresponding families of languages ITL and TL, as well as ITL and CRTL, are incomparable. Additionally we show that ITL is neither closed under complementation nor under intersection.

Extensions. We finally investigate compositions of ITA and other timed models (Section 7). In the first composition, a synchronous product of an ITA and a TA, we prove that the reachability problem becomes undecidable. We then define a more appropriate product of ITA and CRTA. The CRTA part describes a basic task at an implicit additional level 0. For this extended model denoted by ITA<sup>+</sup>, we show that reachability is still decidable with the same complexity and in PSPACE when the number of clocks is fixed.

#### 2 Interrupt Timed Automata

#### 2.1 Notations

The sets of natural, rational and real numbers are denoted respectively by  $\mathbb{N}$ ,  $\mathbb{Q}$  and  $\mathbb{R}$ . A *timed word* over an alphabet  $\Sigma$  is a finite sequence  $w = (a_1, \tau_1) \dots (a_n, \tau_n)$  where  $a_i$  is in  $\Sigma$  and  $(\tau_i)_{1 \leq i \leq n}$  is a non-decreasing sequence of real numbers. The *length* of w is n and the *duration* of w is  $\tau_n$ .

For a finite set X of clocks, a linear expression over X is a term of the form  $\sum_{x \in X} a_x \cdot x + b$  where b and  $(a_x)_{x \in X}$  are in  $\mathbb{Q}$ . We denote by  $\mathcal{C}(X)$  the set of constraints obtained by conjunctions of atomic propositions of the form  $C \bowtie 0$ , where C is a linear expression over X and  $\bowtie \in \{>, \geq, =, \leq, <\}$ . The subset  $\mathcal{C}_0(X)$  of  $\mathcal{C}(X)$  contains constraints of the form  $x + b \bowtie 0$ . An update over X is a conjunction (over X) of assignments of the form  $x := C_x$ , where x is a clock and  $C_x$  is a linear expression over X. The set of all updates over X is written  $\mathcal{U}(X)$ , with  $\mathcal{U}_0(X)$  for the subset containing only assignments of the form x := 0 (reset) or of the form x := x (no update). For a linear expression C and an update u, the expression C[u] is obtained by "applying" u to C, i.e. substituting each x by  $C_x$  in C, if  $x := C_x$  is the update for x in u. For instance, for the set of two clocks  $X = \{x_1, x_2\}$ , expression  $C = x_2 - 2x_1 + 3$  and update u defined by  $x_1 := 1 \land x_2 := 2x_1 + 1$ , applying u to C yields the expression  $C[u] = 2x_1 + 2$ .

A clock valuation is a mapping  $v: X \mapsto \mathbb{R}$ , with  $\mathbf{0}$  the valuation where all clocks have value 0. The set of all clock valuations is  $\mathbb{R}^X$  and we write  $v \models \varphi$  when valuation v satisfies the clock constraint  $\varphi \in \mathcal{C}(X)$ . For a valuation v, a linear expression C and an update u, the value v(C) is obtained by replacing each x in C by v(x) and the valuation v[u] is defined by  $v[u](x) = v(C_x)$  for x in X if  $x := C_x$  is the update for x in u. Observe that an update is performed simultaneously on all clocks. For instance, let  $X = \{x_1, x_2, x_3\}$  be a set of three clocks. For valuation v = (2, 1.5, 3) and update

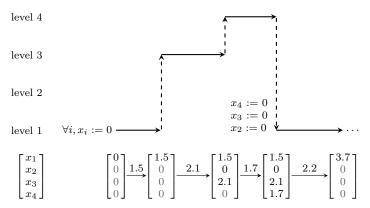

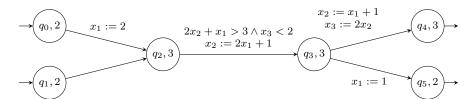

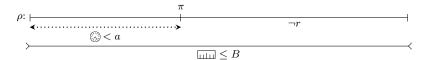

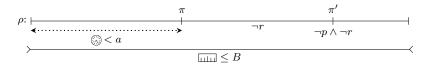

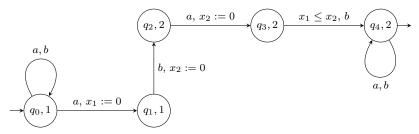

${\bf Fig.~1}~$  Interrupt levels and clocks in an ITA.

u defined by  $x_1 := 1 \land x_2 := x_2 \land x_3 := 3x_2 - x_1$ , applying u to v yields the valuation v[u] = (1, 1.5, 2.5).

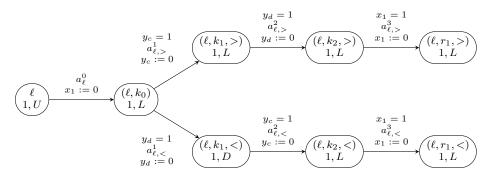

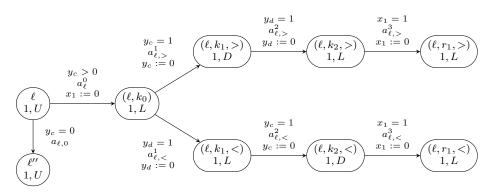

#### 2.2 Models of timed systems

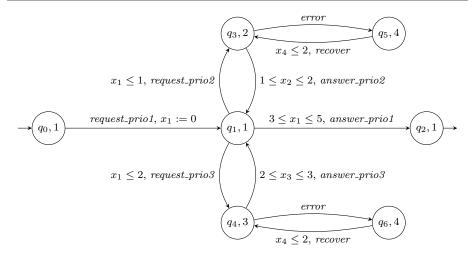

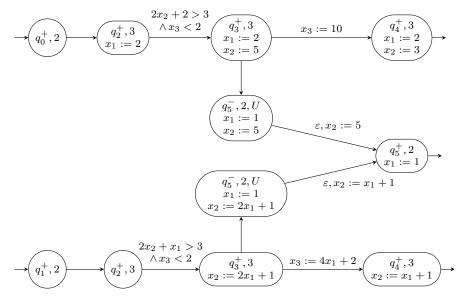

The model of ITA is based on the principle of multi-task systems with interruptions, in a single processor environment. We consider a set of tasks with different priority levels, where a higher level task represents an interruption for a lower level task. At a given level, exactly one clock is active (rate 1), while the clocks for tasks of lower levels are suspended (rate 0), and the clocks for tasks of higher levels are not yet activated and thus contain value 0. The mechanism is illustrated in Fig. 1, where irrelevant clock values are greyed. An example of such behavior can be produced by the ITA depicted in Fig. 2, which describes a system that answer requests according to their priority. It starts by receiving a request for a main task of priority 1. The treatment of this task can be interrupted by tasks of priority 2 or 3, depending on how far the system is in the execution of the main task. Tasks of priority 2 and 3 may generate errors (modeled by an interruption of higher level), after which the system recovers. On this system, deciding if it is possible – or always the case – that the main task is executed in less than a certain amount of time would give an insight on the quality of service of the system.

Enabling of a transition depends on the clocks valuation. The enabling conditions, called *guards*, are linear constraints on the clock values of levels lower than or equal to the current level: the ones that are relevant before the firing of the transition. Additionally, a transition can update the values of the clocks. If the transition decreases (resp. increases) the level, then each clock which is relevant after (resp. before) the transition can either be left unchanged or take a linear expression of clocks of strictly lower level.

Along with its level, each state has a timing policy which indicates whether time may (Lazy, default), may not (Urgent) or must (Delayed) elapse in a state. Note that in TA, this kind of policy can be enforced by an additional clock while this is not possible here because there is a single clock per level. This additional feature is needed for the definition and further use of the model of ITA\_ (see Section 4). Note that the class graph construction of Section 3 is still valid without them.

Fig. 2 An ITA that produces - among others - the behavior represented in Fig. 1.

We also add a labeling of states with atomic propositions, in view of interpreting logic formulas on these automata. In the sequel, the level of a transition is the level of its source state. We also say that a transition is lazy (resp. urgent, delayed) if the policy of its source state is lazy (resp. urgent, delayed).

**Definition 1** An interrupt timed automaton is a tuple  $\mathcal{A} = \langle \Sigma, AP, Q, q_0, F, pol, X, \lambda, lab, \Delta \rangle$ , where:

- $\Sigma$  is a finite alphabet, AP is a set of atomic propositions

- -Q is a finite set of states,  $q_0$  is the initial state,  $F\subseteq Q$  is the set of final states,

- pol:  $Q \rightarrow \{Lazy, Urgent, Delayed\}$  is the timing policy of states,

- $-X = \{x_1, \ldots, x_n\}$  consists of n interrupt clocks,

- the mapping  $\lambda:Q\to\{1,\ldots,n\}$  associates with each state its level and we call  $x_{\lambda(q)}$  the active clock in state q. The mapping  $lab:Q\to 2^{AP}$  labels each state with a subset of AP of atomic propositions,

- $-\Delta\subseteq Q\times \mathcal{C}(X)\times (\Sigma\cup\{\varepsilon\})\times \mathcal{U}(X)\times Q$  is the set of transitions. Let  $q\xrightarrow{\varphi,a,u}q'$  in  $\Delta$  be a transition with  $k=\lambda(q)$  and  $k'=\lambda(q')$ . The guard  $\varphi$  is a conjunction of constraints  $\sum_{j=1}^k a_jx_j+b\bowtie 0$  (involving only clocks from levels less than or equal to k). The update u is of the form  $\wedge_{i=1}^n x_i:=C_i$  with:

- if k > k', *i.e.* the transition decreases the level, then for  $1 \le i \le k'$ ,  $C_i$  is either of the form  $\sum_{j=1}^{i-1} a_j x_j + b$  or  $C_i = x_i$  (unchanged clock value) and for i > k',  $C_i = 0$ :

- if  $k \leq k'$  then for  $1 \leq i \leq k$ ,  $C_i$  is of the form  $\sum_{j=1}^{i-1} a_j x_j + b$  or  $C_i = x_i$ , and for i > k,  $C_i = 0$ .

A configuration  $(q, v, \beta)$  of the associated transition system consists of a state q of the ITA, a clock valuation v and a boolean value  $\beta$  expressing whether time has elapsed since the last discrete transition. This third component is needed to define the semantics according to the policies.

**Definition 2** The semantics of an ITA  $\mathcal{A}$  is defined by the (timed) transition system  $\mathcal{T}_{\mathcal{A}} = (S, s_0, \to)$ . The set S of configurations is  $\{(q, v, \beta) \mid q \in Q, v \in \mathbb{R}^X, \beta \in \{\top, \bot\}\}$ ,

with initial configuration  $s_0 = (q_0, \mathbf{0}, \bot)$ . The relation  $\to$  on S consists of two types of steps:

Time steps: Only the active clock in a state can evolve, all other clocks are suspended. For a state q with active clock  $x_{\lambda(q)}$ , a time step of duration d>0 is defined by  $(q,v,\beta) \xrightarrow{d} (q,v',\top)$  with  $v'(x_{\lambda(q)}) = v(x_{\lambda(q)}) + d$  and v'(x) = v(x) for any other clock x. A time step of duration 0 leaves the system  $\mathcal{T}_{\mathcal{A}}$  in the same configuration. When pol(q) = Urgent, only time steps of duration 0 are allowed from q.

Discrete steps: A discrete step  $(q, v, \beta) \xrightarrow{a} (q', v', \bot)$  can occur if there exists a transition  $q \xrightarrow{\varphi, a, u} q'$  in  $\Delta$  such that  $v \models \varphi$  and v' = v[u]. When pol(q) = Delayed and  $\beta = \bot$ , discrete steps are forbidden.

The labeling function lab is naturally extended to configurations by  $lab(q, v, \beta) = lab(q)$ .

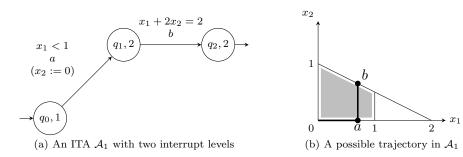

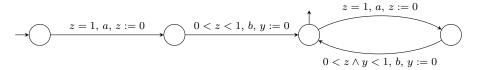

An ITA  $A_1$  is depicted in Fig. 3(a), with two interrupt levels (and two interrupt clocks). A geometric view is given in figure 3(b), with a possible trajectory: first the value of  $x_1$  increases from 0 in state  $q_0$  (horizontal line) and, after transition a occurs, its value is frozen in state  $q_1$  while  $x_2$  increases (vertical line) until reaching the line  $x_2 = -\frac{1}{2}x_1 + \frac{1}{2}$ . The light grey zone defined by  $\left(0 < x_1 < 1, \ 0 < x_2 < -\frac{1}{2}x_1 + \frac{1}{2}\right)$  corresponds to the set of valuations reachable in state  $q_1$  and from which state  $q_2$  is reachable.

Fig. 3 An example of ITA and a possible execution.

We now briefly recall the classical model of Timed Automata (TA) [4] as well as the model of Controlled Real-Time Automata (CRTA) [21]. Note that in both models, timing policies can be enforced by clock constraints.

**Definition 3** A timed automaton is a tuple  $\mathcal{A} = \langle \Sigma, Q, q_0, F, X, \Delta \rangle$ , where  $\Sigma, Q, q_0, F$  are defined as in an ITA, X is a set of clocks and the set of transitions is  $\Delta \subseteq Q \times \mathcal{C}_0(X) \times (\Sigma \cup \{\varepsilon\}) \times \mathcal{U}_0(X) \times Q$ , with guards in  $\mathcal{C}_0(X)$  and updates in  $\mathcal{U}_0(X)$ .

The semantics of a timed automaton is also defined as a timed transition system, with the set  $Q \times \mathbb{R}^X$  of configurations (no additional boolean value). Discrete steps are similar to those of ITA but in time steps, all clocks evolve with same rate 1:  $(q, v) \xrightarrow{d} (q, v')$  iff for each clock x in X, v'(x) = v(x) + d.

Controlled Real-Time Automata extend TA with the following features: the clocks and the states are partitioned according to colors belonging to a set  $\Omega$  and with every state is associated a rational velocity. When time elapses in a state, the set of active clocks (i.e. with the color of the state) evolve with rate equal to the velocity of the state while other clocks remain unchanged. For sake of clarity, we now propose a slightly simplified version of CRTA.

**Definition 4** A CRTA  $\mathcal{A} = (\Sigma, Q, q_0, F, X, up, low, vel, \lambda, \Delta)$  on a finite set  $\Omega$  of colors is defined by:

- $-\Sigma$ , the alphabet of actions,

- -Q, the set of states, with  $q_0 \in Q$  the initial state and  $F \subseteq Q$  the set of final states,

- X the set of clocks,

- mappings up and low associate with each clock respectively an upper and a lower bound.

- $vel : Q \mapsto \mathbb{Q}$  the velocity mapping,

- $-\lambda:X\uplus Q\mapsto\Omega$  the coloring mapping and

- $-\Delta \subseteq Q \times \mathcal{C}_0(X) \times (\Sigma \cup \{\varepsilon\}) \times \mathcal{U}_0(X) \times Q$  the set of transitions, with guards in  $\mathcal{C}_0(X)$  and updates in  $\mathcal{U}_0(X)$ .

Moreover, the lower and upper bound mappings satisfy  $low(x) \leq 0 \leq up(x)$  for each clock  $x \in X$ , and  $low(x) \leq b \leq up(x)$  for each constant b such that  $x \bowtie b$  is a constraint in A.

The original semantics of CRTA is rather involved in order to obtain decidability of the reachability problem. It ensures that entering a state q in which clock x is active, the following conditions on the clock bounds hold: if vel(q) > 0 then  $x \ge low(x)$  and if vel(q) < 0 then  $x \le up(x)$ . Instead (and equivalently) we add a syntactical restriction which ensures this behavior. For instance, if a transition with guard  $\varphi$  and reset u enters state q with vel(q) < 0 and if x is the only clock such that  $\lambda(x) = \lambda(q)$ , then we replace this transition by two other transitions: the first one has guard  $\varphi \wedge x > up(x)$  and adds x := 0 to the reset condition u, the other has guard  $\varphi \wedge x \le up(x)$  and reset u. In the general case where k clocks have color  $\lambda(q)$ , this leads to  $2^k$  transitions. With this syntactical condition, again the only difference from ITA concerns a time step of duration d, defined by  $(q, v) \xrightarrow{d} (q, v')$ , with v'(x) = v(x) + vel(q)d if  $\lambda(x) = \lambda(q)$  and v'(x) = v(x) otherwise.

A run of an automaton  $\mathcal{A}$  in ITA, TA or CRTA is a finite or infinite path in the associated timed transition system  $\mathcal{T}_{\mathcal{A}}$ , where (possibly null) time steps and discrete steps alternate. An accepting run is a finite run starting in  $s_0$  and ending in a configuration associated with a state of F. For such a run with label  $d_1a_1d_2\ldots d_na_n$ , we say that the word  $(a_1,d_1)(a_2,d_1+d_2)\ldots (a_n,d_1+\cdots+d_n)$  (where  $\varepsilon$  actions are removed) is accepted by  $\mathcal{A}$ . The set  $\mathcal{L}(\mathcal{A})$  contains the timed words accepted by  $\mathcal{A}$  and  $Untimed(\mathcal{L}(\mathcal{A}))$ , the untimed language of  $\mathcal{A}$ , contains the projections onto  $\Sigma^*$  of the timed words in  $\mathcal{L}(\mathcal{A})$ . Interrupt Timed Languages or ITL (resp. Timed Languages or TL and Controlled Real-Time Languages or CRTL) denote the family of timed languages accepted by an ITA (resp. a TA and a CRTA).

For instance, the language  $L_1$  accepted by the ITA  $A_1$  in Fig. 3(a) is

$$L_1 = \mathcal{L}(\mathcal{A}_1) = \{(a, \tau)(b, 1 + \frac{\tau}{2}) \mid 0 \le \tau < 1\}.$$

Languages of infinite timed words accepted by Büchi or Muller conditions could be studied but this analysis should address technical issues such as Zeno runs and infinite sequences of  $\varepsilon$ -transitions.

In the context of model-checking, we also consider maximal runs which are either infinite or such that no discrete step is possible from the last configuration. The set of maximal runs starting from configuration s is denoted by Exec(s). Since maximal runs can be finite or infinite, we do not exclude Zeno behaviors. We use the notion of (totally ordered) positions (which allow to consider several discrete actions simultaneously) along a maximal run [25]: for a run  $\rho$ , we denote by  $<_{\rho}$  the strict order over positions. For position  $\pi$  along  $\rho$ , the corresponding configuration is denoted by  $s_{\pi}$ , the prefix of  $\rho$  up to  $\pi$  is written  $\rho^{\leq \pi}$  and its duration,  $Dur\left(\rho^{\leq \pi}\right)$ , is the sum of all delays along the finite run  $\rho^{\leq \pi}$ . Similarly, the suffix of  $\rho$  starting from  $\pi$  is denoted by  $\rho^{\geq \pi}$ . For two positions  $\pi \leq_{\rho} \pi'$ , the subrun of  $\rho$  between these positions is written  $\rho_{[\pi,\pi']}$ , its duration is  $Dur\left(\rho^{\leq \pi'}\right) - Dur\left(\rho^{\leq \pi}\right)$ . The length of  $\rho$ , denoted by  $|\rho|$ , is the number of discrete transitions occurring in  $\rho$ .

#### 3 Regularity of untimed ITL

We prove in this section that the untimed language of an ITA is regular. Similarly to TA (and to CRTA), the proof is based on the construction of a (finite) class graph which is time abstract bisimilar to the transition system  $\mathcal{T}_{\mathcal{A}}$ . This result also holds for infinite words with standard Büchi conditions. As a consequence, we obtain decidability of the reachability problem, as well as decidability for plain  $\mathsf{CTL}^*$  model-checking.

The construction of classes is much more involved than in the case of TA. More precisely, it depends on the expressions occurring in the guards and updates of the automaton (while in TA it depends only on the maximal constant occurring in the guards). We associate with each state q a set of expressions Exp(q) with the following meaning. The values of clocks giving the same ordering of these expressions correspond to a class. In order to define Exp(q), we first build a family of sets  $\{E_k\}_{1\leq k\leq n}$ . Then  $Exp(q)=\bigcup_{k\leq \lambda(q)}E_k$  (recall that  $\lambda(q)$  is the index of the active clock in state q). Finally in Theorem 1 we show how to build the class graph which proves the regularity of the untimed language. This immediately yields a reachability procedure given in Proposition 1.

## 3.1 Construction of $\{E_k\}_{k \le n}$

We first introduce an operation, called *normalization*, on expressions relative to some level. As explained in the construction below, this operation will be used to order expression values at a given level.

**Definition 5 (Normalization)** Let  $C = \sum_{i \leq k} a_i x_i + b$  be an expression over  $X_k = \{x_i \mid i \leq k\}$ , the *k-normalization* of C, norm(C, k), is defined by:

```

- if a_k \neq 0 then \operatorname{norm}(C, k) = x_k + (1/a_k)(\sum_{i < k} a_i x_i + b);

- else \operatorname{norm}(C, k) = C.

```

Since guards are linear expressions with rational constants, we can assume that in a guard  $C\bowtie 0$  occurring in a transition outgoing from a state q with level k, the expression C is either  $x_k+\sum_{i< k}a_ix_i+b$  (by k-normalizing the expression and if necessary changing the comparison operator) or  $\sum_{i< k}a_ix_i+b$ . It is thus written as  $\alpha x_k+\sum_{i< k}a_ix_i+b$ , with  $\alpha\in\{0,1\}$ .

The construction of  $\{E_k\}_{k\leq n}$  proceeds top down from level n to level 1 after initializing  $E_k=\{x_k,0\}$  for all k. As we shall see below, when handling the level k, we add new terms to  $E_i$  for  $1\leq i\leq k$ . These expressions are the ones needed to compute a (pre)order on the expressions in  $E_k$ .

- At level k, first for every expression  $\alpha x_k + \sum_{i < k} a_i x_i + b$  (with  $\alpha \in \{0,1\}$ ) occurring in a guard of an edge leaving a state of level k, we add  $-\sum_{i < k} a_i x_i b$  to  $E_k$ .

- Then we iterate the following procedure until no new term is added to any  $E_i$  for  $1 \le i \le k$ .

- $1 \leq i \leq k.$ 1. Let  $q \xrightarrow{\varphi,a,u} q'$  with  $\lambda(q) \geq k$  and  $\lambda(q') \geq k$ . Let  $C \in E_k$ , then we add C[u] to  $E_k$  (recall that C[u] is the expression obtained by applying update u to C).

- 2. Let  $q \xrightarrow{\varphi,a,u} q'$  with  $\lambda(q) < k$  and  $\lambda(q') \ge k$ . Let C and C' be two different expressions in  $E_k$ . We compute  $C'' = \text{norm}(C[u] C'[u], \lambda(q))$ , choosing an arbitrary order between C and C' in order to avoid redundancy. Let us write C'' as  $\alpha x_{\lambda(q)} + \sum_{i < \lambda(q)} a_i x_i + b$  with  $\alpha \in \{0, 1\}$ . Then we add  $-\sum_{i < \lambda(q)} a_i x_i b$  to  $E_{\lambda(q)}$ .

We illustrate this construction of expressions for the automaton  $\mathcal{A}_1$  of Fig. 3(a). Initially, we have  $E_1 = \{0, x_1\}$  and  $E_2 = \{0, x_2\}$ . When treating level 2, first, expression  $-\frac{1}{2}x_1+1$  is added to  $E_2$  as normalization of the guard  $x_1+2x_2=2$ . Then transition labeled by a updates  $x_2$  (by reseting it to 0). As a result, we have to add to  $E_1$  all differences of expressions of  $E_2$  updated by  $x_2 := 0$ . This only produces expression  $-\frac{1}{2}x_1+1-0$  which is normalized into  $x_1-2$ ; thus expression 2 is added to  $E_1$ . When treating level 1, expression 1 from the guard of transition a is added to  $E_1$ . As a result, we obtain  $E_1 = \{x_1,0,1,2\}$  and  $E_2 = \{x_2,0,-\frac{1}{2}x_1+1\}$ .

**Lemma 1** The construction procedure of  $\{E_k\}_{k\leq n}$  terminates and the size of every  $E_k$  is bounded by  $(E+2)^{2^{n(n-k+1)}+1}$  where E is the size of the edges of the ITA.

Proof Given some k, we prove the termination of the stage relative to k. Observe that the second step only adds new expressions to  $E_{k'}$  for k' < k. Thus the two steps can be ordered. Let us prove the termination of the first step of the saturation procedure. We define  $E_k^0$  as the set  $E_k$  at the beginning of this stage and  $E_k^i$  as this set after insertion of the  $i^{th}$  item in it. With each added item C[u] can be associated its father C. Thus we can view  $E_k$  as an increasing forest with finite degree (due to the finiteness of the edges) and finitely many roots. Assume that this step does not terminate. Then we have an infinite forest and by König lemma, it has an infinite branch  $C_0, C_1, \ldots$  where  $C_{i+1} = C_i[u_i]$  for some update  $u_i$  such that  $C_{i+1} \neq C_i$ . Observe that the number of updates that change the variable  $x_k$  is either 0 or 1 since once  $x_k$  disappears it cannot appear again. We split the branch into two parts before and after this update or we still consider the whole branch if there is no such update. In these (sub)branches, we conclude with the same reasoning that there is at most one update that change the variable  $x_{k-1}$ . Iterating this process, we conclude that the number of updates is at most  $2^k - 1$  and the length of the branch is at most  $2^k$ .

For the sake of readability, we set B = E + 2. The final size of  $E_k$  is thus at most  $E_k^0 \times B^{2^k}$  since the width of the forest is bounded by B.

In the second step, we add at most  $B \times (|E_k| \times (|E_k| - 1))/2$  to  $E_i$  for every i < k. This concludes the proof of termination.

We now prove by a painful backward induction that as soon as  $n \geq 2$ ,  $|E_k| \leq B^{2^{n(n-k+1)}+1}$ . The doubly exponential size of  $E_n$  (proved above) is propagated downwards by the saturation procedure. We define  $p_k = |E_k|$ .

Basis case k=n. We have  $p_n \leq p_n^0 \times B^{2^n}$  where  $p_n^0$  is the number of guards of the outgoing edges from states of level n. Thus  $p_n \leq B \times B^{2^n} = B^{2^n+1} = B^{2^{n(n-n+1)}+1}$  which is the claimed bound.

Inductive case. Assume that the bound holds for  $k < j \le n$ . Due to all executions of the second step of the procedure at strictly higher levels,  $p_k^0$  expressions were added to  $E_k$ , with:

$$\begin{aligned} p_k^0 &\leq B + B \times ((p_{k+1} \times (p_{k+1} - 1))/2 + \dots + (p_n \times (p_n - 1))/2) \\ p_k^0 &\leq B + B \times (B^{2^{n(n-k)+1}+2} + \dots + B^{2^{n+1}+2}) \\ p_k^0 &\leq B \times (n-k+1) \times B^{2^{n(n-k)+1}+2} \\ p_k^0 &\leq B \times B^n \times B^{2^{n(n-k)+1}+2} \quad \text{(here we use } B \geq 2) \\ p_k^0 &\leq B^{2^{n(n-k)+1}+n+3} \end{aligned}$$

Taking into account the first step of the procedure for level k, we have:

$$p_k \le B^{2^{n(n-k)+1} + 2^k + n + 3}.$$

Let us consider the term  $\delta = 2^{n(n-k+1)} + 1 - (2^{n(n-k)+1} + 2^k + n + 3)$ . Since k < n,

$$\delta \ge (2^{n-1} - 1)2^{n(n-k)+1} - (2^k + n + 2)$$

$$\delta \ge (2^{n-1} - 1)2^{n(n-k)+1} - (2^{n-1} + 2^n)$$

$$\delta \ge (2^{n-1} - 1)2^{n(n-k)+1} - 2^{n+1} \ge 0$$

Thus  $p_k \leq B^{2^{n(n-k)+1}+2^k+n+3} \leq B^{2^{n(n-k+1)}+1} = (E+2)^{2^{n(n-k+1)}+1}$  which is the claimed bound.  $\square$

#### 3.2 Construction of the class automaton

In order to analyze the size of the class automaton defined below, we recall and adapt a classical result about partitions of n-dimensional Euclidian spaces.

**Definition 6** Let  $\{H_k\}_{1\leq k\leq m}$  be a family of hyperplanes of  $\mathbb{R}^n$ . A region defined by this family is a connected component of  $\mathbb{R}^n\setminus\bigcup_{1\leq k\leq m}H_k$ . An extended region defined by this family is a connected component of  $\bigcap_{k\in I}H_k\setminus\bigcup_{k\notin I}H_k$  where  $I\subseteq\{1,\ldots,m\}$ .

**Proposition 1** ([39]) The number of regions defined by the family  $\{H_k\}_{1 \leq k \leq m}$  is at  $most \sum_{i=0}^{n} {m \choose i}$ .

We derive from this proposition:

Corollary 1 The number of extended regions defined by the family  $\{H_k\}_{1 \leq k \leq m}$  is at  $most \sum_{p=0}^{n} {m \choose p} \sum_{i=0}^{n-p} {m-p \choose i} \leq e^2 m^n$ .

*Proof* Observe that an extended region is a region belonging to an intersection of at most n hyperplanes (by removing redundant hyperplanes). Thus counting the number of such intersections and applying the previous proposition yields the following formula:

$$\sum_{p=0}^{n} \binom{m}{p} \sum_{i=0}^{n-p} \binom{m-p}{i} \leq \sum_{p=0}^{n} \frac{m^p}{p!} \sum_{i=0}^{n-p} \frac{m^{n-p}}{i!} = m^n \sum_{p=0}^{n} \frac{1}{p!} \sum_{i=0}^{n-p} \frac{1}{i!} \leq e^2 m^n$$

**Theorem 1** The untimed language of an ITA is regular.

*Proof* First, we assume that the policy of every state is lazy. At the end of the proof, we explain how to adapt the construction for states with urgent or delayed policies.

Class definition. Let  $\mathcal{A}$  be an ITA with E transitions and n clocks, the decision algorithm is based on the construction of a (finite) class graph which is time abstract bisimilar to the transition system  $\mathcal{T}_{\mathcal{A}}$ . A class is a syntactical representation of a subset of reachable configurations. More precisely, it is defined as a pair  $R = (q, \{\leq_k\}_{1 \leq k \leq \lambda(q)})$  where q is a state and  $\leq_k$  is a total preorder over  $E_k$ , for  $1 \leq k \leq \lambda(q)$ .

The class R describes the set of configurations:

$$[\![R]\!] = \{(q, v, \beta) \mid \beta \in \{\top, \bot\}, \ \forall k \le \lambda(q) \ \forall (g, h) \in E_k, \ g[v] \le h[v] \ \text{iff} \ g \le_k h\}$$

The initial state of this graph is defined by the class  $R_0$  with  $[\![R_0]\!]$  containing  $(q_0, \mathbf{0}, \bot)$  which can be straightforwardly determined. For example, for ITA  $\mathcal{A}_1$  of Fig. 3(a), the initial class is  $R_0 = (q_0, Z_0)$  with  $Z_0 : x_1 = 0 < 1 < 2$ . The final states are all  $R = (q, \{ \le_k \}_{1 \le k \le \lambda(q)})$  with  $q \in F$ .

Observe that fixing a state, the set of configurations  $[\![R]\!]$  of a non empty class R is exactly an extended region associated with the hyperplanes defined by the comparison of two expressions of some  $E_k$ . Since  $(E+2)^{2^{n^2}+1}$  is an upper bound of the number of expressions of any level,  $m=(E+2)^{2^{n^2+1}+2}$  is an upper bound of the number of hyperplanes. So using Corollary 1, the number of semantically different classes for a given state is bounded by:

$$e^2 m^n = e^2 (E+2)^{2^{n^2+1}n+2n}$$

Since one can test semantical equality between classes in polynomial time w.r.t. their size [36], we implicitely consider in the sequel of the proof classes modulo the semantical equivalence.

As usual, there are two kinds of transitions in the graph, corresponding to discrete steps and time steps.

Discrete step. Let  $R=(q,\{\leq_k\}_{1\leq k\leq \lambda(q)})$  and  $R'=(q',\{\leq_k'\}_{1\leq k\leq \lambda(q')})$  be two classes. There is a transition  $R \xrightarrow{e} R'$  for a transition  $e: q \xrightarrow{\varphi, a, u} q'$  if there is some  $(q, v) \in [\![R]\!]$ and  $(q',v') \in [\![R']\!]$  such that  $(q,v) \xrightarrow{e} (q',v')$ . In this case, for all  $(q,v) \in [\![R]\!]$  there is a  $(q', v') \in [R']$  such that  $(q, v) \xrightarrow{e} (q', v')$ . This can be decided as follows.

*Firability condition.* Write  $\varphi = \bigwedge_{j \in J} C_j \bowtie_j 0$ . Since we assumed normalized guards, for every j,  $C_j = \alpha x_k + \sum_{i < k} a_i x_i + b$  (with  $\alpha \in \{0, 1\}$  and  $k = \lambda(q)$ ). By construction  $C'_j = -\sum_{i < \lambda(q)} a_i x_i - b \in E_k$ . For each  $j \in J$ , we define a condition depending on  $\bowtie_j$ . For instance, if  $C_j \leq 0$ , we require that  $\alpha x_k \leq_k C'_j$ , or if  $C_j > 0$  we require that  $\alpha x_k \npreceq_k C'_j \land C'_j \preceq \alpha x_k.$

**Successor definition.** R' is defined as follows. Let  $k \leq \lambda(q')$  and  $g', h' \in E_k$ .

- 1. Either  $k \leq \lambda(q)$ , by construction,  $g'[u], h'[u] \in E_k$  then  $g' \leq_k' h'$  iff  $g'[u] \leq_k h'[u]$ .

- 2. Or  $k > \lambda(q)$ , let  $D = g'[u] h'[u] = \sum_{i \le \lambda(q)} c_i x_i + d$ , and  $C = \text{norm}(D, \lambda(q))$ , and write  $C = \alpha x_{\lambda(q)} + \sum_{i < \lambda(q)} a_i x_i + b$  (with  $\alpha \in \{0,1\}$ ). By construction  $C' = -\sum_{i < \lambda(q)} a_i x_i - b \in E_{\lambda(q)}.$

When  $c_{\lambda(q)} \geq 0$  then  $g' \preceq'_k h'$  iff  $\alpha x_{\lambda(q)} \preceq_{\lambda(q)} C'$ . When  $c_{\lambda(q)} < 0$  then  $g' \preceq'_k h'$  iff  $C' \preceq_{\lambda(q)} \alpha x_{\lambda(q)}$ .

By definition of  $[\![\cdot]\!]$ ,

- For any  $(q, v) \in [R]$ , if there exists  $(q, v) \xrightarrow{e} (q', v')$  then the firability condition is fulfilled and (q', v') belongs to [R'].

- If the firability condition is fulfilled then for each  $(q, v) \in [R]$  there exists  $(q', v') \in$  $[\![R']\!]$  such that  $(q,v) \xrightarrow{e} (q',v')$ .

Time step. Let  $R = (q, \{ \leq_k \}_{1 \leq k \leq \lambda(q)})$ . There is a transition  $R \xrightarrow{succ} Post(R)$  for  $Post(R) = (q, \{ \leq'_k \}_{1 \leq k \leq \lambda(q)}), \text{ the time successor of } R, \text{ which is defined as follows.}$

For every  $i < \lambda(q) \preceq_i' = \preceq_i$ . Let  $\sim$  be the equivalence relation  $\preceq_{\lambda(q)} \cap \preceq_{\lambda(q)}^{-1}$  induced by the preorder. On equivalence classes, this (total) preorder becomes a (total) order. Let V be the equivalence class containing  $x_{\lambda(q)}$

- 1. Either  $V=\{x_{\lambda(q)}\}$  and it is the greatest equivalence class. Then  $\preceq'_{\lambda(q)}=\preceq_{\lambda(q)}$  (thus Post(R)=R).

- 2. Either  $V = \{x_{\lambda(q)}\}$  and it is not the greatest equivalence class. Let V' be the next equivalence class. Then  $\leq'_{\lambda(q)}$  is obtained by merging V and V', and preserving  $\leq_{\lambda(q)}$  elsewhere.

- 3. Either V is not a singleton. Then we split V into  $V \setminus \{x_{\lambda(q)}\}$  and  $\{x_{\lambda(q)}\}$  and "extend"  $\preceq_{\lambda(q)}$  by  $V \setminus \{x_{\lambda(q)}\} \preceq'_{\lambda(q)} \{x_{\lambda(q)}\}.$

By definition of  $[\![\cdot]\!]$ , for each  $(q,v)\in[\![R]\!]$ , there exists d>0 such that  $(q,v+d)\in$  $\llbracket Post(R) \rrbracket$  and for each d with  $0 \le d' \le d$ , then  $(q, v + d') \in \llbracket R \rrbracket \cup \llbracket Post(R) \rrbracket$ .

We now explain how the policy is handled. Given a state q such that pol(q) = U, for every class  $R = (q, \{ \leq_k \}_{1 \leq k \leq \lambda(q)})$  we delete the time steps outgoing from R. The case of a state q such that pol(q) = D, is a little bit more involved. First we partition classes between time open classes, where for every every configuration of the class there exists a small amount of time elapse that let the new configuration in the same class, and

time closed classes. The partition is performed w.r.t. the equivalence class V of  $x_{\lambda(q)}$  for the relation  $\sim$  (see above in the proof). The class R is time open iff  $V=\{x_{\lambda(q)}\}$ . Then we successively replace every time closed class R by two copies  $R^-$  and  $R^+$ , which capture wether time has elapsed since the last last discrete step. Thus, a time edge entering R is redirected towards  $R^+$  while a discrete edge entering R is redirected towards  $R^-$ . A time step  $R \xrightarrow{succ} R'$  is replaced by two transitions  $R^- \xrightarrow{succ} R'$  and  $R^+ \xrightarrow{succ} R'$ , while a discrete step  $R \xrightarrow{e} R'$  is replaced by the transition  $R^+ \xrightarrow{e} R'$ . Time open classes allow time elapsing, hence no splitting is required for these classes.

Since there is at most one time edge outgoing from a class, the number of edges of the new graph is at most twice the number of edges in the original graph.  $\Box$

**Proposition 2** The reachability problem for Interrupt Timed Automata is decidable and belongs to 2-EXPTIME and PTIME when the number of clocks is fixed.

Proof The reachability problem is solved by building the class graph and applying standard reachability algorithm. Since the number of semantically different classes is at most doubly exponential in the size of the model and the semantical equivalence can be checked in polynomial time w.r.t. the size of the class (also doubly exponential) this leads to a 2-EXPTIME complexity. When the number of clocks is fixed the size of the graph is at most polynomial w.r.t. the size of the problem leading to a PTIME procedure. No complexity gain can be obtained by a non deterministic search without building the graph since the size of the graph is only polynomial w.r.t. the size of a class. □

Remarks. This result should be contrasted with the similar one for TA. The reachability problem for TA is PSPACE-complete and thus less costly to solve than for ITA. However, fixing the number of clocks does not reduce the complexity for TA (when this number is greater than or equal to 3) while this problem belongs now to PTIME for ITA. Summarizing, the main source of complexity for ITA is the number of clocks, while in TA it is the binary encoding of the constants [20].

Since the construction of the graph depends on a set of expressions, there is no notion of *granularity* as in Timed Automata. When the only guards are comparisons to constants and the only updates resets of clocks (as in Timed Automata), the abstraction obtained is coarser than the region abstraction of [4]: it consists only in products of intervals.

## 3.3 Example

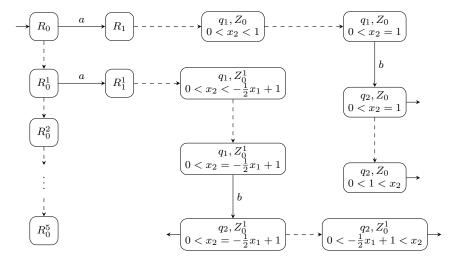

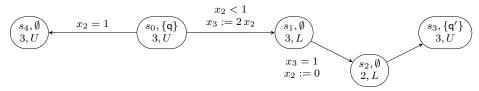

We illustrate this construction of a class automaton for the automaton  $\mathcal{A}_1$  of Fig. 3(a). The resulting class automaton is depicted on Fig. 4, where dashed lines indicate time steps.

Recall that we obtained  $E_1 = \{x_1, 0, 1, 2\}$  and  $E_2 = \{x_2, 0, -\frac{1}{2}x_1 + 1\}$ . In state  $q_0$ , the only relevant clock is  $x_1$  and the initial class is  $R_0 = (q_0, Z_0)$  with  $Z_0 : x_1 = 0 < 1 < 2$ . Its time successor is  $R_0^1 = (q_0, Z_0^1)$  with  $Z_0^1 : 0 < x_1 < 1 < 2$ . Transition a leading to  $q_1$  can be taken from both classes, but not from the next time successors  $R_0^2 = (q_0, 0 < x_1 = 1 < 2), R_0^3 = (q_0, 0 < 1 < x_1 < 2), R_0^4 = (q_0, 0 < 1 < x_1 = 2),$  or  $R_0^5 = (q_0, 0 < 1 < 2 < x_1)$ .

Fig. 4 The class automaton for  $A_1$

Transition a switches from  $R_0$  to  $R_1=(q_1,Z_0,x_2=0<1)$ , because  $x_1=0$ , and from  $R_0^1$  to  $R_1^1=\left(q_1,Z_0^1,x_2=0<-\frac{1}{2}x_1+1\right)$ . Transition b is fired from those time successors for which  $x_2=-\frac{1}{2}x_1+1$ .

On the geometric view of figure 3(b), the displayed trajectory corresponds to the following path in the class automaton:

$$R_0 \to R_0^1 \xrightarrow{a} R_1^1 \to \left(q_1, Z_0^1, 0 < x_2 < -\frac{1}{2}x_1 + 1\right) \to \left(q_1, Z_0^1, 0 < x_2 = -\frac{1}{2}x_1 + 1\right)$$

$$\xrightarrow{b} \left(q_2, Z_0^1, 0 < x_2 = -\frac{1}{2}x_1 + 1\right)$$

### 4 A simpler model

## 4.1 Definition of ITA\_

We introduce a restricted version of ITA, called ITA\_, which is interesting both from a theoretical and a practical point of view. When modeling interruptions in real-time systems, the clock associated with some level measures the time spent in this level or more generally the time spent by some tasks at this level. Thus when going to a higher level, this clock is not updated until returning to this level. The ITA\_ model takes this feature into account. Moreover, it turns out that the reachability problem for ITA\_ can be solved more efficiently. This also provides a better complexity upper-bound for the reachability problem on ITA (in the general case).

**Definition 7** The subclass ITA\_ of ITA is defined by the following restriction on updates. For a transition  $q \xrightarrow{\varphi,a,u} q'$  of an automaton  $\mathcal{A}$  in ITA\_ (with  $k = \lambda(q)$  and  $k' = \lambda(q')$ ), the update u is of the form  $\wedge_{i=1}^n x_i := C_i$  with:

- if k > k', then for  $1 \le i \le k'$ ,  $C_i := x_i$  and for  $k' + 1 \le i \le n$ ,  $C_i = 0$ , i.e. the only updates are the resets of now irrelevant clocks;

– if  $k \leq k'$  then  $C_k$  is of the form  $\sum_{j=1}^{k-1} a_j x_j + b$  or  $C_k = x_k$ . For  $k < i \leq k', C_i = 0$ and  $C_i = x_i$  otherwise.

Thus, complex updates appear only in transitions increasing the level, and only for the active clock of the transition level.

The proof of the following result is based on Propositions 3 and 5 proved in the next two sections.

**Theorem 2** The reachability problem for ITA belongs to NEXPTIME.

*Proof* Given an ITA  $\mathcal{A}$  with transitions of size E and constants coded over b bits, we build the ITA<sub>-</sub>  $\mathcal{A}'$  of Proposition 3. Then we apply on  $\mathcal{A}'$  the reachability procedure of Proposition 5. In this procedure, we consider paths of length bounded by  $(E'+n)^{3n}$ , where E' is the number of transitions of  $\mathcal{A}'$ . Since  $E' \leq 2^{4b \cdot E \cdot n^2}$  (as shown in the proof of Proposition 3), the length of the paths considered is bounded by

$$(E'+n)^{3n} \le (2^{4b \cdot E \cdot n^2} + n)^{3n} \le (n+2)^{12b \cdot E \cdot n^3}$$

which establishes the claimed upper bounds.  $\Box$

#### 4.2 From ITA to ITA\_

In this subsection we prove that ITA and ITA\_ are equivalent w.r.t. the associated (timed) languages.

**Proposition 3** Given an ITA A, we build an automaton A' in ITA\_ accepting the same timed language and with the same clocks such that its number of edges (resp. states) is exponential w.r.t. the number of edges (resp. states) in A and polynomial when the number of clocks is fixed.

*Proof* Starting from ITA  $\mathcal{A} = \langle \Sigma, AP, Q, q_0, F, pol, X, \lambda, lab, \Delta \rangle$ , the construction of automaton  $\mathcal{A}'$  relies on memorizing at a given level i, for every clock  $x_i$  at a lower level, an expression depending on  $x_1, \ldots, x_{j-1}$ , corresponding to the delayed update of  $x_i$ . This expression is used later to replace the value of  $x_i$  in guards and to restore its correct value by update after decreasing to level j.

To this aim we associate with every pair of levels  $i \geq j$ , a set of expressions  $F_{i,j}$ inductively defined by:

- $\begin{array}{l} -\ F_{i,i} = \{x_i\} \\ -\ \forall i > j\ F_{i,j} = F_{i-1,j} \cup \{e[\{x_k \leftarrow e_k\}_{k < j}] \mid e \text{ is the expression of an update of } x_j \text{ by an edge of level } i \text{ and } \forall k,\ e_k \in F_{i,k}\} \end{array}$

We write  $F_j = F_{n,j} = \bigcup_{i=j}^n F_{i,j}$ . The set  $F_j$  thus contains all expressions of updates of  $x_i$  that appear at higher levels.

Although the number of expressions is syntactically doubly exponential w.r.t. the number of clocks, one can show that the number of distinct expressions is only singly exponential.

First we assume that ITA A has only integral constants, the case of rational constants is handled at the end of the proof. It can be shown that every expression  $e_k$  of  $F_k$  can be written

$$e_k = \sum_{i_0, \dots, i_p \in \operatorname{sub}(k)} \alpha_{k, i_p} \cdot \alpha_{i_p, i_{p-1}} \cdots \alpha_{i_1, i_0} \cdot x_{i_0}$$

with the convention that  $x_0$  is the constant 1, and where  $\mathrm{sub}(k)$  is the set of all (ordered) subsequences of  $0, \ldots, k-1$  and  $\alpha_{j,i}$  is the coefficient of  $x_i$  in some update of  $x_j$ .

For the family  $\alpha$  of all integers  $\alpha_{j,i}$ , assume that these constants are coded over  $b_{\alpha}$  bits each (including the sign of the coefficient). The expression  $x_{i_0}$  can also be coded into an integer of  $\log_2(n)$  bits (with a special symbol to indicate that it is the expression of a clock rather than a constant). Let  $b = \max(b_{\alpha}, \log_2(n) + 1)$  be the (maximal) number of bits used to code a coefficient. Then each term of the sum is a product of at most k such coefficients, therefore can be coded with kb bits. Summing at most  $2^k$  such products yields an integer that can be coded over kb + k bits. Thus there can be at most  $2^{k(b+1)}$  different expressions in  $E_k$ .

Automaton  $\mathcal{A}'$  is then defined as follows.

- The set of states is

$$Q' = \{ (q^+, e_1, \dots, e_{i-1}) \mid q \in Q, \ \lambda(q) = i \text{ and } \forall j, \ e_j \in F_j \} \\ \cup \{ (q^-, e_1, \dots, e_i) \mid q \in Q, \ \lambda(q) = i \text{ and } \forall j, \ e_j \in F_j \},$$

with  $pol(q^+, e_1, ..., e_{i-1}) = pol(q)$  and  $pol(q^-, e_1, ..., e_i) = U$ . Note that the sequence is empty if i = 1. Moreover:

$$\lambda(q^+, e_1, \dots, e_{i-1}) = \lambda(q^-, e_1, \dots, e_i) = \lambda(q).$$

- The initial state of  $\mathcal{A}'$  is  $(q_0^+, x_1, \dots, x_{i-1})$  if  $\lambda(q_0) = i$ . The final states of  $\mathcal{A}'$  are the states with first component  $q^+$  for  $q \in F$ .

Let  $q \xrightarrow{\varphi, a, u} q'$  be a transition in  $\mathcal{A}$  such that  $\lambda(q) = i$ ,  $\lambda(q') = i'$  and u is defined by  $\bigwedge_{j=1}^{i} x_j := C_j$ .

- If  $i \leq i'$ , then for every  $(q^+, e_1, \dots, e_{i-1})$  there is a transition

$$(q^+, e_1, \dots, e_{i-1}) \xrightarrow{\varphi', a, u'} (q'^+, e'_1, \dots, e'_{i'-1})$$

in  $\mathcal{A}'$  with  $\varphi' = \varphi(\{x_j \leftarrow e_j\}_{j < i})$ , update u' is defined by  $x_i := C_i[\{x_j \leftarrow e_j\}_{j < i}]$ ; for all j < i,  $e'_j = C_j[\{x_k \leftarrow e_k\}_{k < i}]$  and for all j such that  $i \le j < i'$ ,

• If i > i' then for every  $(q^+, e_1, \dots, e_{i-1})$  there is a transition

$$(q^+, e_1, \dots, e_{i-1}) \xrightarrow{\varphi', a, u'} (q'^-, e'_1, \dots, e'_{i'})$$

in  $\mathcal{A}'$  with  $\varphi' = \varphi(\{x_j \leftarrow e_j\}_{j < i})$ , update u' contains only the trivial updates  $x_j := x_j$  for all clocks and for all  $j \le i'$ ,  $e_j' = C_j[\{x_k \leftarrow e_k\}_{k < i}]$ .

• For every  $(q^-, e_1, \ldots, e_i)$  there is in  $\mathcal{A}'$  a transition

$$(q^-, e_1, \dots, e_i) \xrightarrow{true, \varepsilon, x_i := e_i} (q^+, e_1, \dots, e_{i-1}).$$

In words, given a transition, the guard is modified according to these expressions. The modification of the update consists only in applying the update at the current level and taking into account the other updates in the expressions labeling the destination state. When the transition increases the level, the expression associated with a new "frozen" clock  $(x_j \text{ for } i \leq j < i')$  is the clock itself. The urgent states  $(q^-, -)$  are introduced for handling the case of a transition that decreases the level. In this case, one reaches such a state that memorizes also the expression of the clock at the current level. Note that the memorized expressions can correspond to an update proceeded

at any (higher) level. From this state a single transition must be (immediately) taken whose effect is to perform the update corresponding to the memorized expression.

It is routine to check that the languages of the two automata are identical. Each transition in  $\mathcal{A}$  is replaced by several transitions in  $\mathcal{A}'$ , which number is bounded by the number of expressions that can be attached to the source of the original transition. In addition, transitions decreasing level are further "split" through states  $(q^-, -)$ . Thus the number E' of transitions in  $\mathcal{A}'$  is bounded by

$$E' \le 2 \cdot E \cdot |F_n|^n$$

$$\le 2 \cdot E \cdot \left(2^{n(b(E+1)+1)}\right)^n$$

$$\le 2 \cdot E \cdot 2^{n^2(b(E+1)+1)}$$

$$\le 2^{n^2(b(E+1)+1)+1+\log_2(E)}$$

$$\le 2^{n^2((b+1)(E+1)+1)}$$

$$\le 2^{4b \cdot E \cdot n^2}$$

(provided  $E \ge 2$ ). This yields the exponential complexity for the number of transitions. The case of the number of states is similar.

In the case when there are rational constants, assume each constant is coded with a pair (r,d) of numerator and denominator. Assume each r and d can be coded over b bits. We compute the  $lcm\ \delta$  of all denominators: since there are at most E constants (E, the size of  $\Delta$  contains the number of guards and updates),  $\delta$  can be coded over Eb bits. We consider ITA  $A_{\delta}$  which is A where all constants are multiplied by  $\delta$ . Thus a constant of  $A_{\delta}$  is an integer that can be coded over b' = Eb + b = b(E+1) bits. The above bound on the number of expressions applies on  $A_{\delta}$ . Note that after the construction of  $A'_{\delta}$ , A' can be obtained by dividing each constant in  $A'_{\delta}$  by  $\delta$ .  $\square$

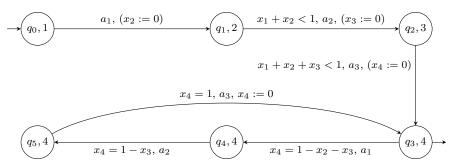

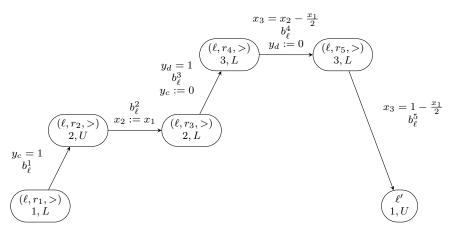

Example. We illustrate this construction on ITA  $A_2$  of Fig. 5. The sets of expressions are computed as on Table 1 and the resulting ITA\_  $A'_2$  is depicted on Fig. 6.

Fig. 5 ITA  $A_2$  containing updates of frozen clocks

The translation above of an ITA into an equivalent ITA\_ induces an exponential blowup. The proposition below shows that the bound is reached.

**Proposition 4** There exist a family  $\{A_n\}_{n\in\mathbb{N}}$  of ITA with two states, n clocks and constants coded over b bits, where b is polynomial in n, such that the equivalent ITA\_built by the procedure above has a number of states greater than or equal to  $2^n$ .

Fig. 6 ITA<sub>-</sub>  $\mathcal{A}_2'$  equivalent to  $\mathcal{A}_2$

| $i \setminus j$ | 1               | 2                                                                             | 3         |

|-----------------|-----------------|-------------------------------------------------------------------------------|-----------|

| 1               | $\{x_1\}$       |                                                                               |           |

| 2               | $\{x_1, 2\}$    | $\{x_2\}$                                                                     |           |

| 3               | $\{x_1, 2, 1\}$ | $\{x_2, 2x_1+1, 5, 3, x_1+1, 3, 2\}$                                          | $\{x_3\}$ |

|                 |                 |                                                                               | ĺ         |

|                 |                 | $q_2 \xrightarrow{x_2 := 2x_1 + 1} q_3  q_3 \xrightarrow{x_2 := x_1 + 1} q_4$ |           |

**Table 1** Sets of expressions  $F_{i,j}$  for  $A_2$ .

Proof For  $n \in \mathbb{N}$ , let  $\mathcal{A}_n$  be the ITA with n clocks and two states  $q_{\text{init}}$  (initial) and q (final) both of level n (and lazy policy) built as follows. There is a transition from  $q_{\text{init}}$  to q with update  $\bigwedge_{k=1}^n x_k := 1$  that sets all clocks to 1. For  $1 \leq k \leq n$  there are two loops on q with updates  $x_k := x_{k-1}$  and  $x_k := \alpha_k x_{k-1}$  respectively, where  $\alpha_k$  is the kth prime number (and with the convention that  $x_0$  is the constant 1).

When building the sets of expressions, no expressions are added until level n, since all updates occur at this level. At level k,  $F_{n,k}$  contains (at least)  $2^k$  expressions: all possible products of the first k prime numbers, namely

$$F_{n,k}\supset\left\{\prod_{i\in I}\alpha_i\;\middle|\; I\subseteq\{1,\ldots,k\}\right\}.$$

Indeed, at level 1,  $F_{n,1}=\{x_1,1,2\}$ . Now assume that  $F_{n,k-1}$  contains all products  $\prod_{i\in I}\alpha_i$  where  $I\subseteq\{1,\ldots,k-1\}$ . By update  $x_k:=x_{k-1},\,F_{n,k}\supset F_{n,k-1}$ . By update  $x_k:=\alpha_kx_{k-1},\,F_{n,k}$  contains all products  $\alpha_k\prod_{i\in I}\alpha_i=\prod_{i\in I\uplus\{k\}}\alpha_i$ . Therefore

$$F_{n,k} \supset \left\{ \prod_{i \in I} \alpha_i \mid I \subseteq \{1, \dots, k-1\} \right\} \cup \left\{ \prod_{i \in I \uplus \{k\}} \alpha_i \mid I \subseteq \{1, \dots, k-1\} \right\}$$

$$F_{n,k} \supset \left\{ \prod_{i \in I} \alpha_i \mid I \subseteq \{1, \dots, k\} \right\}.$$

The expressions thus built are distinct, since they are products of distinct prime numbers. Remark that the set of expression for level k is in bijection with a sequence of updates  $x_1 := \dots, x_2 := \dots, x_k := \dots$ , the choice of the update depending on the choice of the set I.

Therefore all expressions of  $F_{n,n}$  are reached (in association with state q) and the set of states in  $\mathcal{A}'_n$  is at least of size  $2^n$ . In addition, it should be noted that the nth prime number is in  $O(n \log_2(n))$ , therefore can be coded over  $O(\log_2(n)^2)$  bits. So the size of the constants appearing in the updates (and the size of the representation of  $\mathcal{A}_n$ ) is polynomial in n while the representation of  $\mathcal{A}'_n$  is exponential in n.

## 4.3 Reachability on ITA\_

In this section we use counting arguments to obtain an upper bound for the reachability problem on  $ITA_-$ .

The following counting lemma does not depend on the effect of the updates but only on the timing constraints induced by the policies.

**Lemma 2 (Counting Lemma)** Let  $\mathcal{A}$  be an  $ITA_-$  with E transitions and n clocks, then in a sequence  $(e_1, \ldots, e_l)$  of transitions of  $\mathcal{A}$  where  $l > (E+n)^{3n}$ , there exist i < j with  $e_i = e_j$  such that the level of any transition  $e_k$  with  $i \le k \le j$  is greater than or equal to the level of  $e_i$ , say p, and:

- either  $e_i$  updates  $x_p$ ,

- either no  $e_k$  with  $i \leq k \leq j$  updates  $x_p$  and  $e_i$  is delayed or lazy.

- or no  $e_k$  with  $i \le k \le j$  updates  $x_p$  and no time elapses for clock  $x_p$  between  $e_i$  and  $e_j$ .

*Proof* Assume that the conclusions of the lemma are not satisfied, we claim that  $l \leq (E+2n)^{3n}$ .

First we prove that the number of transitions of level m that occur between two occurrences of transitions of strictly lower level is less than or equal to  $(E+2)^3$ . Indeed there can be no more than E occurrences of transitions that update  $x_m$ . Then between two such transitions (or before the first or after the last) there can be no more than E lazy or delayed transitions of level m that do not update  $x_m$ . Finally between any kind of previous transitions (or before the first or after the last), there can be no more than E urgent transitions that do not update  $x_m$ , since they prevent time from elapsing at level m.

Summing up, there can be no more than  $E + E(E+1) + E(E(E+1)+1) \le (E+1)^3$  transitions of level m that occur between two occurrence of transitions of strictly lower level.

Now we prove by induction that the number of transitions at level less than or equal to m is at most  $(E+m)^{3m}$ . This is true for m=1 by the previous proof. Assume the formula valid for m, then grouping the transitions of level m+1 between the occurrences of transition of lower level (or before the first or after the last), we obtain that the number of transitions at levels less than or equal to m+1 is at most:

$$(E+m)^{3m} + ((E+m)^{3m} + 1)(E+1)^3 \le (E+m)^{3m+3} + 2(E+m)^{3m}$$

$\le (E+m+1)^{3(m+1)}$

**Proposition 5** The reachability problem for  $ITA_-$  belongs to NEXPTIME. More precisely, reachability can be checked over paths with length less than or equal to  $(E+n)^{3n}$ , where E is the number of transitions and n is the number of clocks.

Proof Let  $\mathcal{A}=(\Sigma,Q,q_0,F,pol,X,\lambda,\Delta)$  be an ITA\_ with n clocks. Let  $E=|\Delta|$  be the number of transitions of  $\mathcal{A}$ . Assume that there is a run of minimal length  $\rho$  from  $(q_0,v_0)$  to some configuration  $(q_f,v_f)$ . Suppose now that  $|\rho|>B=(E+n)^{3n}$ . We will build a run  $\rho'$  from  $(q_0,v_0)$  to  $(q_f,v_f)$  that is strictly smaller, hence contradicting the minimality hypothesis.

Since  $|\rho| > B$ , then one of the three cases of Lemma 2 applies. Therefore there is a transition e at level k repeated twice, from positions  $\pi$  and  $\pi'$  and separated by a subrun  $\sigma$  containing only transitions of level higher than or equal to k. Moreover:

- Either e updates  $x_k$ . In this case, all clocks have the same value after the first and the second occurrence of e. Hence removing  $e\sigma = \rho_{[\pi,\pi'[}$  from  $\rho$  yields a valid run  $\rho'$  of  $\mathcal{A}$  reaching  $(q_f,v_f)$ . Run  $\rho'$  is strictly smaller than  $\rho$ , since  $e\sigma$  which is of length at least 1 was removed.

- Either no update occurred for  $x_k$  and e is delayed or lazy. In this case, upon reaching  $\pi'$ , the clocks of level i < k have retained the same value, while  $x_k$  has increased by  $Dur\left(\rho_{[\pi,\pi']}\right)$ . Hence when replacing  $e\sigma = \rho_{[\pi,\pi']}$  by a time step of duration  $Dur\left(\rho_{[\pi,\pi']}\right)$ , the configuration in  $\pi'$  is unchanged. In addition, since e was delayed or lazy, this time step is allowed in  $\mathcal{A}$ , and this yields a shorter run of  $\mathcal{A}$

- Or no update occurred and  $\pi$  and  $\pi'$  are at the same instant (separated by instantaneous actions). In this case, all clocks of level smaller than or equal to k again have the same value after the first and the second occurrence of e. Again removing  $\rho_{[\pi,\pi'[}$  yields a smaller run.

The decision procedure is as follows. It non deterministically guesses a path in the ITA\_ whose length is less than or equal to the bound. In order to check that this path yields a run, it builds a linear program whose variables are  $\left\{x_i^j\right\}$ , where  $x_i^j$  is the value of clock  $x_i$  after the jth step, and  $\{d_j\}$  where  $d_j$  is the amount of time elapsed during the jth step, when j corresponds to a time step. The equations and inequations are deduced from the guards and updates of discrete transitions in the path and the delay of the time steps. The size of this linear program is exponential w.r.t. the size of the ITA\_. As a linear program can be solved in polynomial time [36], we obtain a procedure in NEXPTIME.  $\square$

One could wonder whether the class graph construction would lead to a better complexity when applied on  $ITA_-$ . Unfortunately, the number of expressions occurring in the class graph while being smaller than for ITA is still doubly exponential w.r.t. the size of the model.

## 5 Timed model-checking

First observe that model-checking CTL\* formulas on ITA can be done with classical procedures on the class graph previously built. We now consider verification of real time formulas.

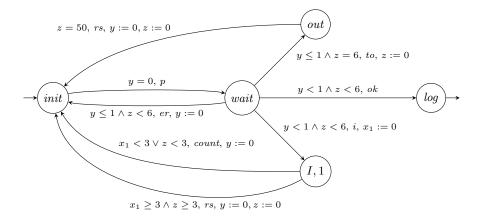

In the case of linear time, the logic LTL has been extended into the Metric Temporal Logic (MTL) [27], by adding time intervals as constraints to the U modality. However, MTL suffers from undecidability of the model-checking problem on TA. Hence decidable fragments have been proposed, such as Metric Interval Temporal Logic (MITL) [5], which prohibits the use of point intervals (of the form [a,a]). Later, MITL was restricted into State Clock Logic (SCL) [35], in order to obtain more efficient verification procedures. Model-checking MITL (thus SCL) on TA is decidable. Unfortunately, we show here that model-checking SCL (thus MITL) on ITA is undecidable. For this, we reduce the halting problem on a two counter machine into model-checking an SCL formula on an ITA.

Concerning branching time logics, at least two different timed extensions of CTL have been proposed. The first one [2] also adds time intervals to the U modality while the (more expressive) second one considers formula clocks [25]. Model-checking timed automata was proved decidable in both cases and compared expressiveness was revisited later on [14].

We conjecture that model-checking of TCTL is undecidable when using two (or more) formula clocks. Indeed, as shown in Section 7.1, the reachability problem in a product of an ITA and a TA with two clocks is undecidable, thus prohibiting model-checking techniques through automaton product and reachability testing as in [1]. However, contrary to what is claimed in [10], this is not enough to yield an undecidability proof.

Two fragments for which model-checking is decidable on ITA have nonetheless been identified. The first one,  $\mathsf{TCTL}_c^{\mathsf{int}}$ , accepts only internal clocks (from the automaton on which the formulas will be evaluated) as formula clocks. The second one,  $\mathsf{TCTL}_p$ , restricts the nesting of  $\mathsf{U}$  modalities. We provide verification procedures in both cases.

## 5.1 Undecidability of State Clock Logic

We first consider the timed extension of linear temporal logic, and more particularly the SCL fragment [35].

$\textbf{Definition 8} \ \ \text{Formulas of the timed logic SCL are defined by the following grammar:}$

$$\psi = p \mid \psi \land \psi \mid \neg \psi \mid \psi \cup \psi \mid \psi \cup \psi \mid \Diamond_{\bowtie a} \psi \mid \Diamond_{\bowtie a} \psi$$

where  $p \in AP$  is an atomic proposition,  $\bowtie \in \{>, \geq, =, \leq, <\}$ , and a is a rational number.

We use the usual shorthands **t** for  $\neg(p \land \neg p)$ ,  $\forall \psi$  for  $\forall \psi$ ,  $\forall \psi$  for  $\neg(\forall \psi)$  and  $\forall \psi$  for  $\neg(\varphi \land \neg \psi)$ .

The semantics are defined in the usual manner for boolean operators and U. The S modality is the past version of U. Modality  $\triangleright_{\bowtie a} \psi$  is true if the *next* time  $\psi$  is true will occur in a delay that respects the condition  $\bowtie a$ . Similarly,  $\triangleleft_{\bowtie a} \psi$  is true if the *last* time  $\psi$  was true occurred in a (past) delay that respects the condition  $\bowtie a$ . More

formally, for an execution  $\rho$ , we inductively define  $(\rho, \pi) \models \varphi$  by:

```

\begin{array}{lll} (\rho,\pi) \models p & \text{iff} & \rho \in lab(s_\pi) \\ (\rho,\pi) \models \varphi \wedge \psi & \text{iff} & (\rho,\pi) \models \varphi \text{ and } (\rho,\pi) \models \psi \\ (\rho,\pi) \models \neg \varphi & \text{iff} & (\rho,\pi) \not\models \varphi \\ (\rho,\pi) \models \varphi \cup \psi & \text{iff} & \text{there is a position } \pi' \geq_\rho \pi \text{ such that } (\rho,\pi') \models \psi \\ & \text{and for all } \pi'' \text{ s.t. } \pi \leq_\rho \pi'' <_\rho \pi', \ (\rho,\pi'') \models \varphi \vee \psi \\ (\rho,\pi) \models \varphi \cup \psi & \text{iff} & \text{there is a position } \pi' \leq_\rho \pi \text{ such that } (\rho,\pi') \models \psi \\ & \text{and for all } \pi'' \text{ s.t. } \pi \geq_\rho \pi'' >_\rho \pi', \ (\rho,\pi'') \models \varphi \vee \psi \\ (\rho,\pi) \models \triangleright_{\bowtie a} \varphi & \text{iff} & \text{either } (\rho,\pi) \models \varphi \text{ and } 0 \bowtie a \\ & \text{or, there is a position } \pi' >_\rho \pi \text{ such that } (\rho,\pi') \models \varphi, \\ & Dur(\rho_{[\pi,\pi']}) \bowtie a \text{ and for all } \pi'' \text{ s.t. } \pi \leq_\rho \pi'' <_\rho \pi', (\rho,\pi'') \not\models \varphi \\ (\rho,\pi) \models \triangleleft_{\bowtie a} \varphi & \text{iff} & \text{either } (\rho,\pi) \models \varphi \text{ and } 0 \bowtie a \\ & \text{or, there is a position } \pi' <_\rho \pi \text{ such that } (\rho,\pi') \models \varphi, \\ & Dur(\rho_{[\pi',\pi]}) \bowtie a \text{ and for all } \pi'' \text{ s.t. } \pi \geq_\rho \pi'' >_\rho \pi', (\rho,\pi'') \not\models \varphi \end{array}

```

Given an ITA  $\mathcal{A}$  and an SCL formula  $\varphi$ ,  $\mathcal{A} \models \varphi$  if for all executions  $\rho$  of  $\mathcal{A}$ ,  $(\rho, \pi_0) \models \varphi$ , where  $\pi_0 = 0$  is the initial position of  $\rho$ .

**Theorem 3** Model checking SCL over ITA is undecidable. Specifically, there exists a fixed formula using only modalities U and  $\trianglelefteq_{=a}$  such that checking its truth over ITA with 3 levels is undecidable.

*Proof* We build an ITA and an SCL formula that together simulate a deterministic two counter machine. More specifically, we define a formula  $\varphi_{2cm}$  such that given a two counter machine  $\mathcal{M}$ , we can build an ITA  $\mathcal{A}_{\mathcal{M}}$  with three clocks such that  $\mathcal{A}_{\mathcal{M}} \models \varphi_{2cm}$  if and only if  $\mathcal{M}$  does not halt.

Recall that such a machine  $\mathcal{M}$  consists of a finite sequence of labeled instructions, which handle two counters c and d, and ends at a special instruction with label Halt. The other instructions have one of the two forms below, where  $e \in \{c, d\}$  represents one of the two counters:

```

-e := e + 1; goto \ell'

-\text{ if } e > 0 \text{ then } (e := e - 1; \text{ goto } \ell') \text{ else goto } \ell''

```

Without loss of generality, we may assume that the counters have initial value zero. The behavior of the machine is described by a (possibly infinite) sequence of configurations:  $\langle \ell_0, 0, 0 \rangle \langle \ell_1, n_1, p_1 \rangle \dots \langle \ell_i, n_i, p_i \rangle \dots$ , where  $n_i$  and  $p_i$  are the respective counter values and  $\ell_i$  is the label, after the  $i^{th}$  instruction. The problem of termination for such a machine ("is the *Halt* label reached?") is known to be undecidable [32].

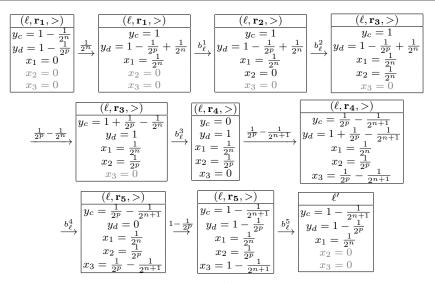

The idea of the encoding is that, provided the execution satisfies the formula, clocks of level 1 and 2 keep the values of c and d indifferently, by  $x_i = \frac{1}{2^n}$  if n is the value of a counter e. Level 3 will be used as the working level. Transmitting the value of clocks to lower levels, prohibited in the ITA model, will be enforced by SCL formulas. In the sequel, we will define:

- a module  $A_{\leftrightarrow}$  and a formula  $\varphi_{\leftrightarrow}$  such that the values contained in clocks  $x_1$  and  $x_2$  at the beginning of an execution  $\rho$  are swapped if and only if  $(\rho, 0) \models \varphi_{\leftrightarrow}$ ,

- a module  $\mathcal{A}_+$  and a formula  $\varphi_+$  such that if the value of  $x_2$  is  $\frac{1}{2^n}$  at the beginning of an execution  $\rho$ , then  $x_2$  has value  $\frac{1}{2^{n+1}}$  if and only if  $(\rho,0) \models \varphi_+$ ,

- a module  $\mathcal{A}_{-}$  and a formula  $\varphi_{-}$  such that if the value of  $x_2$  is  $\frac{1}{2^n}$  with n > 0 at the beginning of an execution  $\rho$ , then  $x_2$  has value  $\frac{1}{2^{n-1}}$  if and only if  $(\rho, 0) \models \varphi_{-}$ .

Joining these modules according to  $\mathcal{M}$  yields an ITA. Combining the formulas (independently of  $\mathcal{M}$ ), we obtain an SCL formula that is satisfied if some execution, while complying to the formulas of the modules, reaches the final state. Both constructions are explained in details after the definitions below.

Let us define formulas  $Span_1 = \mathbf{q}' \Rightarrow \triangleleft_{=1} \mathbf{q}$  and  $Span_2 = \mathbf{p}' \Rightarrow \triangleleft_{=2} \mathbf{p}$  where  $\mathbf{p}, \mathbf{p}', \mathbf{q}, \mathbf{q}'$  are propositional variables. Let  $x_1^0$  and  $x_2^0$  denote the respective values of  $x_1$  and  $x_2$  upon entering a given module.

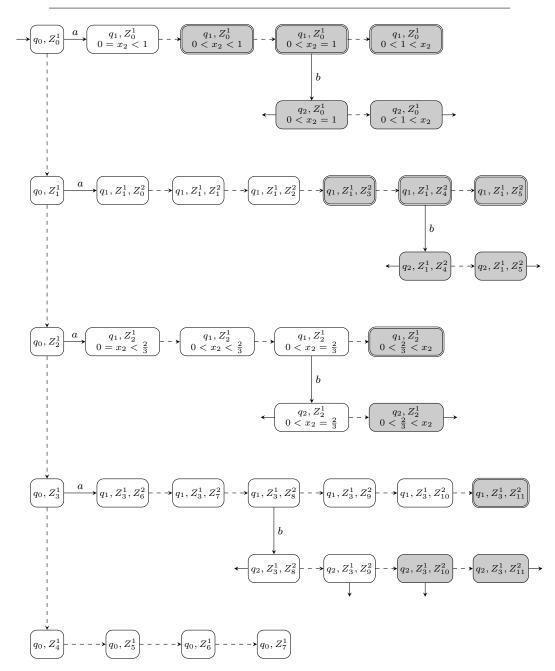

Swapping module. The module  $\mathcal{A}_{\leftrightarrow}$  that swaps the values of  $x_1$  and  $x_2$  is depicted in Fig. 7. Note that this module does not actually swap the values of  $x_1$  and  $x_2$  for every execution. However, by imposing that state  $q_{end}$  is reached exactly 2 time units after  $q_0$  (or  $q'_0$ ) was left, and that  $q_4$  (resp.  $q'_4$ ) is reached exactly 1 t.u. after  $q_1$  (resp.  $q'_1$ ) was left, the values of  $x_1$  and  $x_2$  will be swapped. This requirement can be expressed in SCL by  $\varphi_{\leftrightarrow} = \mathsf{G}$  ( $Span_1 \land Span_2$ ). Let  $w_i$  be the time elapsed in state  $q_i$ , for an execution  $\rho$  of  $\mathcal{A}_{\leftrightarrow}$  that satisfies  $\varphi_{\leftrightarrow}$ . Note that  $q_{start}$  and  $q_{end}^{\neq}$  are all urgent, hence no time can elapse in these states. We shall therefore consider only what happens in the swapping submodules. We detail only the case when  $x_2 > x_1$ , the case when  $x_2 < x_1$  is analogous. The ITA constraints provide:

$$\begin{array}{ll} w_0 = 0 & \qquad & (q_0 \text{ is urgent}) \\ w_1 = x_2^0 - x_1^0 & \qquad & (\text{update } x_3 := x_1 \text{ and guard } x_3 = x_2) \\ w_2 = 1 - x_2^0 & \qquad & (\text{guard } x_3 = 1) \\ w_4 = 0 & \qquad & (q_4 \text{ is urgent}) \end{array}$$

The time spent between the last instant  $\mathbf{q}$  was satisfied (upon leaving  $q_1$ ) and the only instant when  $\mathbf{q}'$  is true (upon entering  $q_4$ ) is exactly the time spent in states  $q_2$  and  $q_3$ . Similarly, the time between the last instant  $\mathbf{p}$  was satisfied (leaving  $q_0$ ) and the instant  $\mathbf{p}'$  is true (when reaching  $q_{end}^{\neq}$ ) is the total amount of time spent in  $q_1, q_2, q_3, q_4$ , and  $q_5$ . Hence, if  $\varphi_{\leftrightarrow}$  is satisfied then:

$$\begin{aligned} w_2 + w_3 &= 1 & \qquad \left( \mathsf{q}' \Rightarrow \triangleleft_{=1} \mathsf{q} \right) \\ w_1 + w_2 + w_3 + w_4 + w_5 &= 2 & \qquad \left( \mathsf{p}' \Rightarrow \triangleleft_{=2} \mathsf{p} \right) \end{aligned}$$

Hence  $w_3=x_2^0$  and  $w_5=1-w_1=x_1^0-\left(x_2^0-1\right)$ . Since upon entering  $q_3$ , clock  $x_1$  has value 0, when leaving,  $x_1$  has value  $x_2^0$ . Similarly, when entering  $q_5$ ,  $x_2$  has value  $x_1-1=x_2^0-1$ , therefore  $x_2$  has value  $x_1^0$  when reaching  $q_{end}^{\neq}$ . Note that this module swaps  $x_1$  and  $x_2$  regardless of their coding a counter value.

Incrementation module. The same idea applies for the incrementation module  $\mathcal{A}_+$  of Fig. 8. We force the time spent in total in  $r_1$  and  $r_2$  is one, expressed in SCL by  $\varphi_+ = \mathsf{G}\,Span_1$ . The guards and updates in  $\mathcal{A}_+$  ensure that, with the same notation as above, time spent in  $r_1$  will be  $1-\frac{1}{2}x_2^0$ . Hence, when reaching  $r_3$ , clock  $x_2$  will have value  $\frac{1}{2}x_2^0$ . Therefore, if  $x_2^0 = \frac{1}{2^n}$ , coding a counter of value n, at the end of  $\mathcal{A}_+$ ,  $x_2$  has value  $\frac{1}{2^{n+1}}$ , thus coding a value n+1 for the same counter.

**Decrementation module.** Decrementation, for which the corresponding module is depicted on Fig. 9, is handled in a similar manner (with  $\varphi_{-} = \varphi_{+} = \mathsf{G}\,Span_{1}$ ). The only difference is that  $x_{2}$  has to be compared to 1 in order to test if the value of the counter encoded by  $x_{2}$  is 0.

(a) Choice submodule.

(b) Swapping submodule  $(x_2 > x_1)$ .

(c) Swapping submodule  $(x_2 < x_1)$ .

Fig. 7 Swapping module  $\mathcal{A}_{\leftrightarrow}$ . Submodules are connected through identical states  $(q_0, q_0', q_{end}')$ .

Fig. 8 Incrementation module.

Fig. 9 Decrementation module.

Since the constraints in  $Span_1$  (and  $Span_2$ ) are equalities, they can be satisfied only if q' (and p') are true at a single point in time.

Automaton  $\mathcal{A}_{\mathcal{M}}$  is then defined as the concatenation of modules according to  $\mathcal{M}$ . For clarity, a state  $(q, \ell)$  denotes state q in a module corresponding to instruction  $\ell$ .